一、主要失效原因分類

MOSFET失效可以分為外部應力損傷、電路設計缺陷、製造工藝缺陷三大類,具體表現如下:

(一)外部應力損傷

1.靜電放電(ESD)擊穿

·成因:MOSFET柵源極(G-S)間電容極小(幾pF)、輸入阻抗極高(10⁹Ω+),少量靜電電荷(如人體、環境摩擦產生)透過公式 U=Q/C 可生成數百伏高壓,直接擊穿G-S絕緣層。

·典型場景:未接地的操作環境、化纖衣物摩擦、乾燥環境下的器件搬運。

我哋都知道,雖然管子有抗靜電嘅保護措施,但仍然要小心對待。喺儲存同運輸過程中,最好用金屬容器或者導電材料包裝,唔好放喺容易產生靜電高壓嘅化工材料或者化纖織物入面。組裝、調試嘅時候,工具、儀表、工作台等都應該良好接地。要防止操作人員嘅靜電干擾造成嘅損壞,例如唔宜穿尼龍、化纖衣服,手或者工具喺接觸集成塊之前最好先接一下地。對器件引線矯直彎曲或者人工焊接嘅時候,使用嘅設備必須良好接地。

2.過流、過壓、過溫

·成因:

○過流:輸入端保護二極管電流容限僅約1mA,瞬態電流超過10mA(如浪涌、負載突變)時,二極管過熱燒毀,失去保護作用。

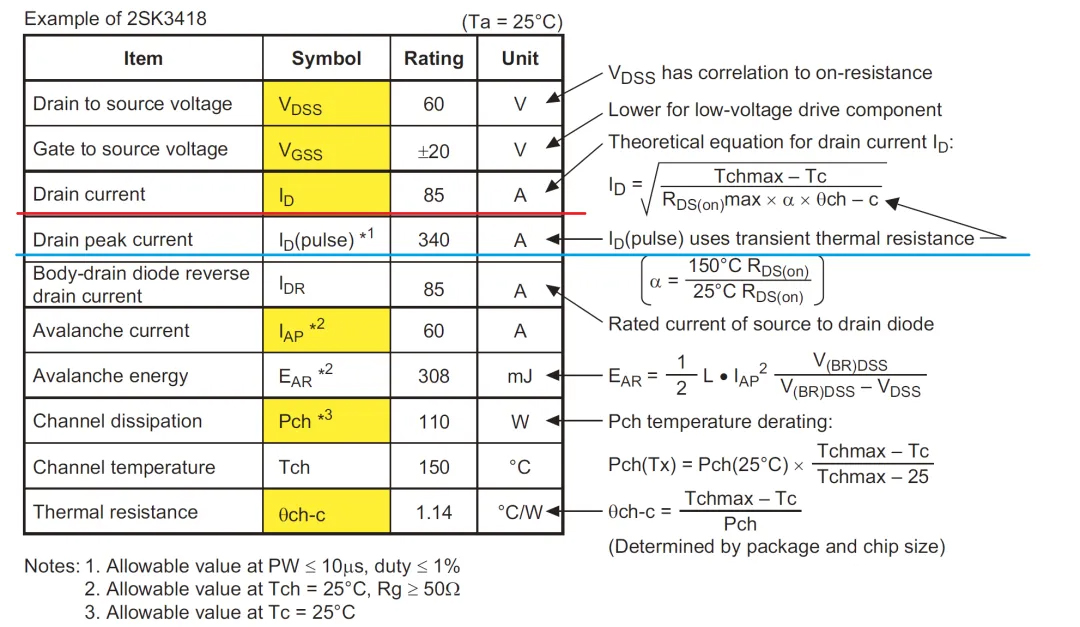

○過壓:柵極電壓超過額定值(如驅動電路故障),導致氧化層擊穿;漏源極(D-S)間電壓超過耐壓值(VDS),引發雪崩擊穿。

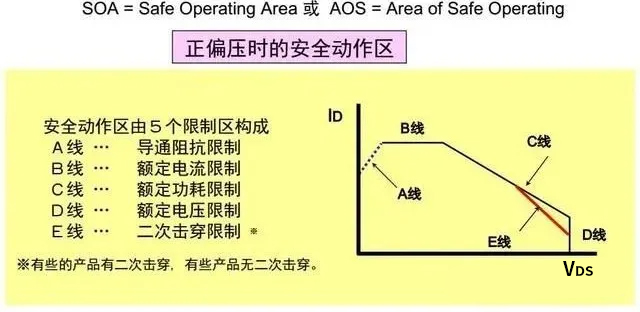

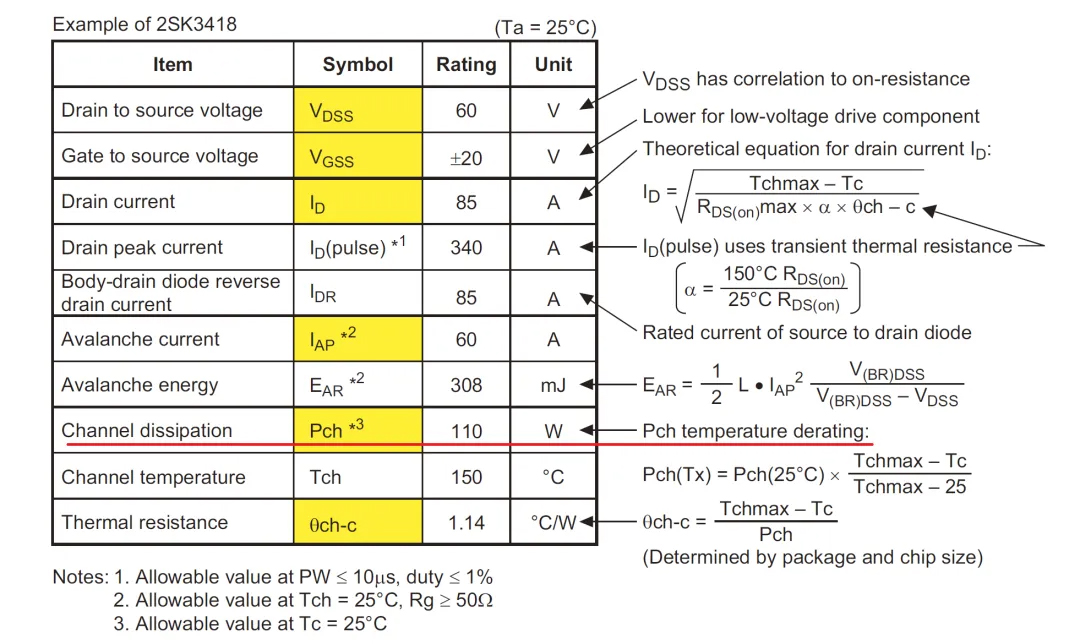

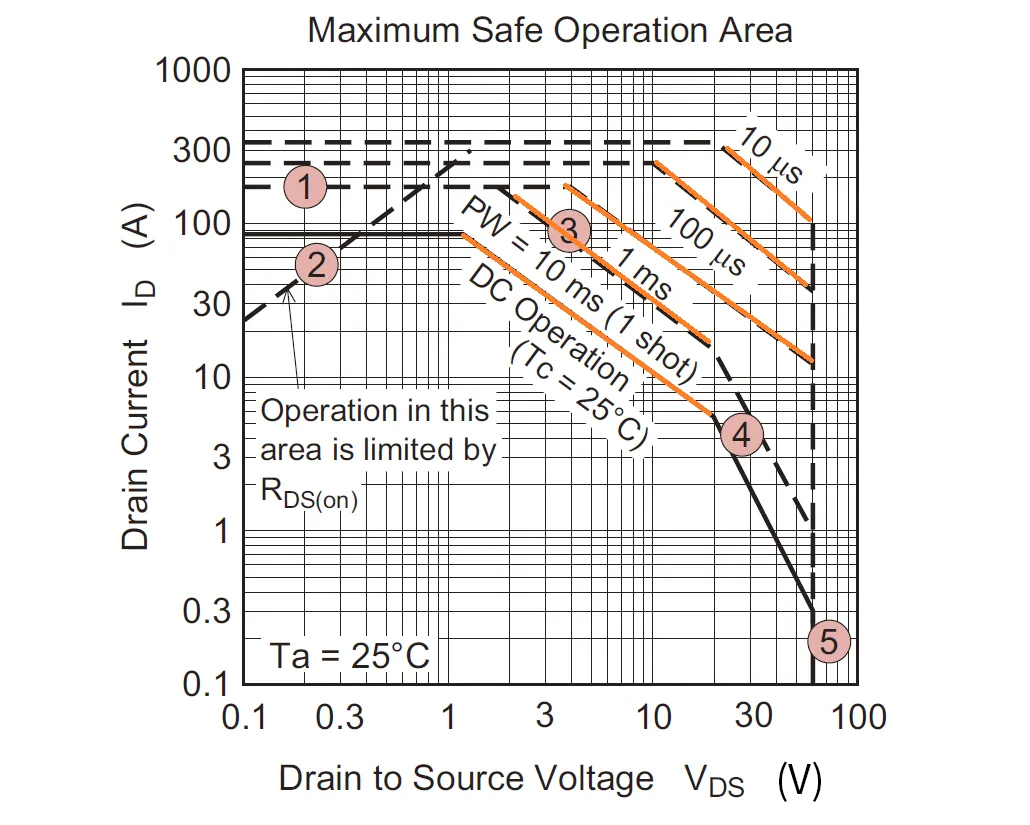

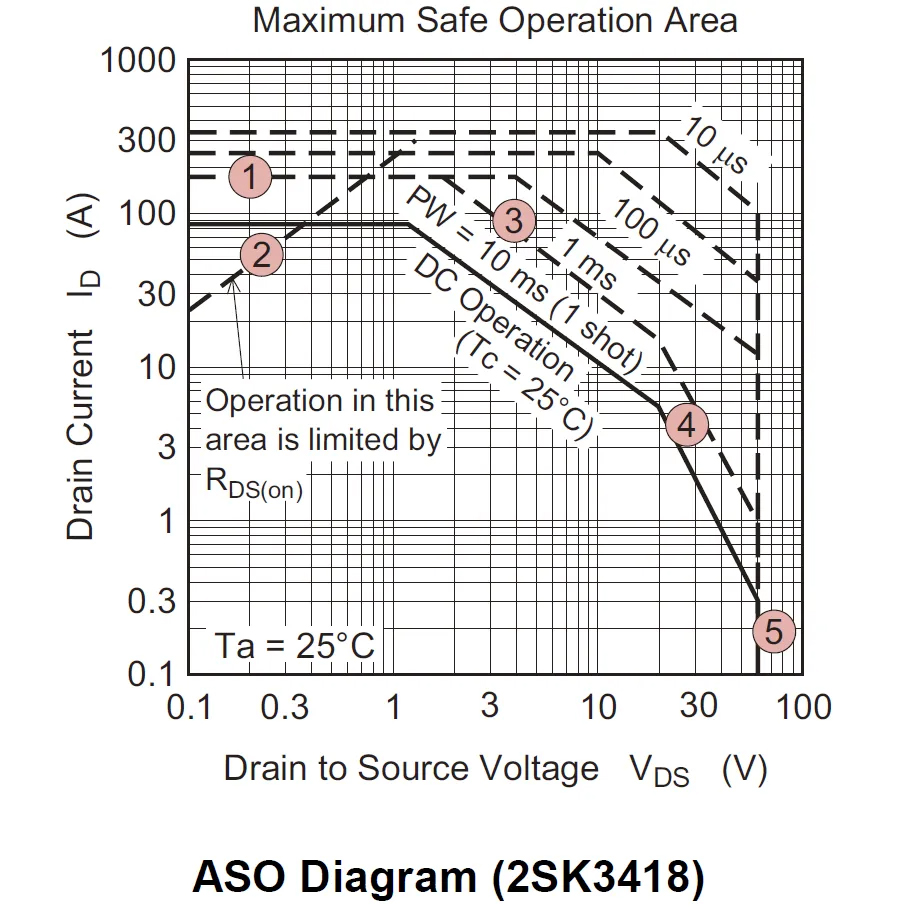

有啲廠家將佢稱之為 “Area of Safe Operation (ASO)”。

安全工作區:SOA(Safe Operating Area)係由一系列(電壓,電流)坐標點形成嘅一個二維區域,開關器件正常工作時嘅電壓同電流都唔會超過該區域。簡單噉講,只要器件工作喺SOA區域入面就係安全嘅,超過呢個區域就存在危險。

SOA(Safe Operating Area)係指安全工作區,由一系列限制條件組成嘅一個漏源極電壓VDS同漏極電流ID嘅二維坐標圖,開關器件正常工作時嘅電壓同電流都唔應該超過該限定範圍。

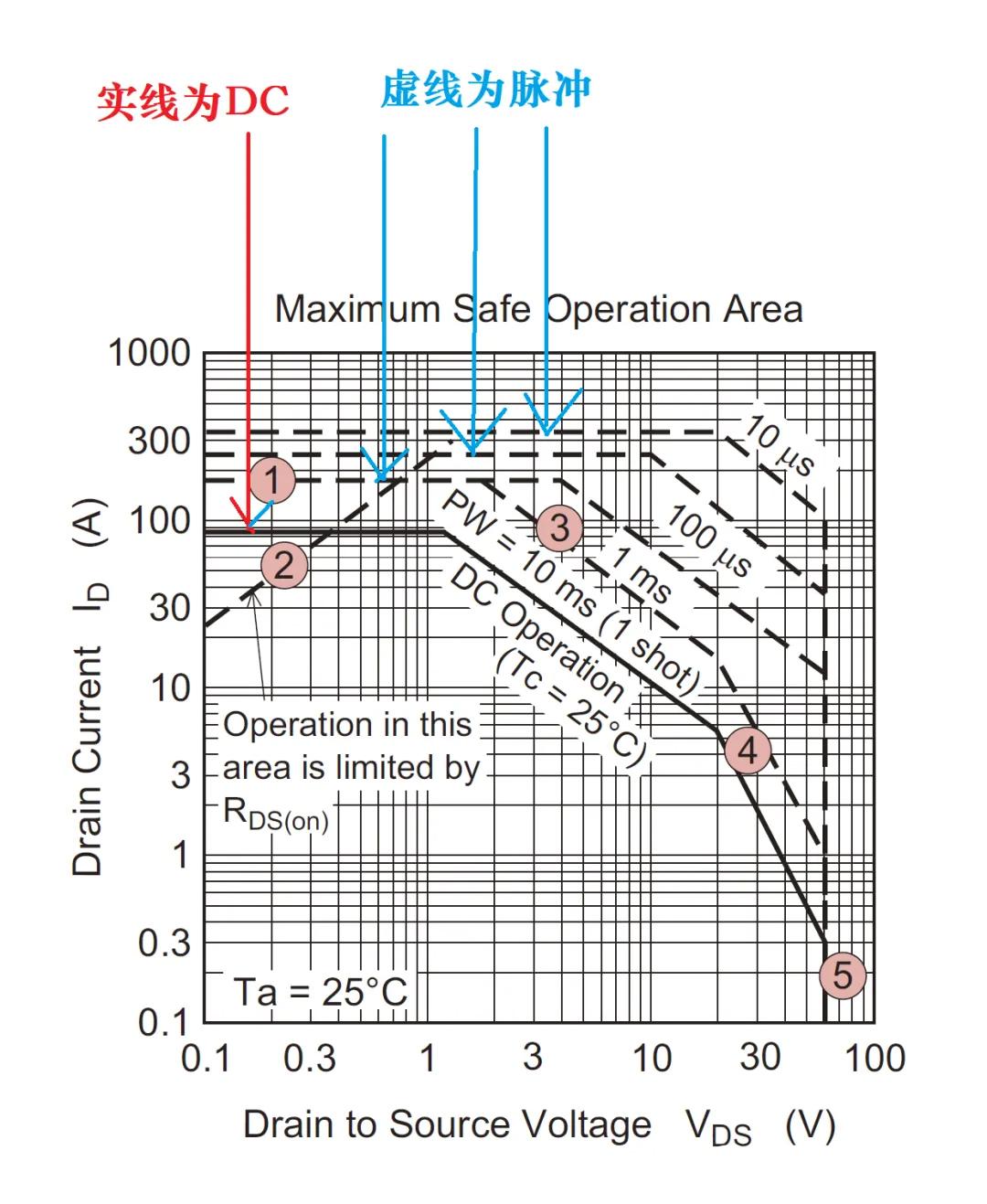

SOA區域分為以下5個區域:

·A線:係由導通電阻RDS(on)max [ID = VDS / RDS(on)]限制嘅區域。呢個區域一般同ASO區域分開討論。因為喺固定嘅VGS電壓同環境條件下,功率MOSFET嘅RDS(ON)係固定嘅,所以呢條斜線嘅斜率為1/R(DS(ON))。

·B線:係受最大額定電流IDC(穩態直流)、ID(pulse)(脈衝)max限制嘅區域。即係:Ids能夠承載最大電流限制嘅線。

需要注意嘅係IDM係脈衝工作狀態嘅最大電流IDC,通常最大漏極脈衝電流IDM為連續漏極電流ID嘅3到4倍,所以脈衝電流要遠高過連續嘅直流電流。

·C線:係受通道損耗(Channel dissipation或者Channel loss,ID流經DS係主要功率產生嘅功耗)限制嘅區域,電流同電壓嘅乘積嘅最大值,即額定功耗限制嘅線路。

正如我哋注意到嘅咁,呢條線帶有一個恆定嘅斜率,但係一個負斜率。佢係恆定嘅,因為呢條SOA功率限制線上嘅每一個點都承載相同嘅恆定功率,由公式P = IV表示。

所以喺呢個SOA對數曲線入面,呢個會產生-1嘅斜率。負號係因為流過MOSFET嘅電流隨著漏源電壓嘅增加而減少。

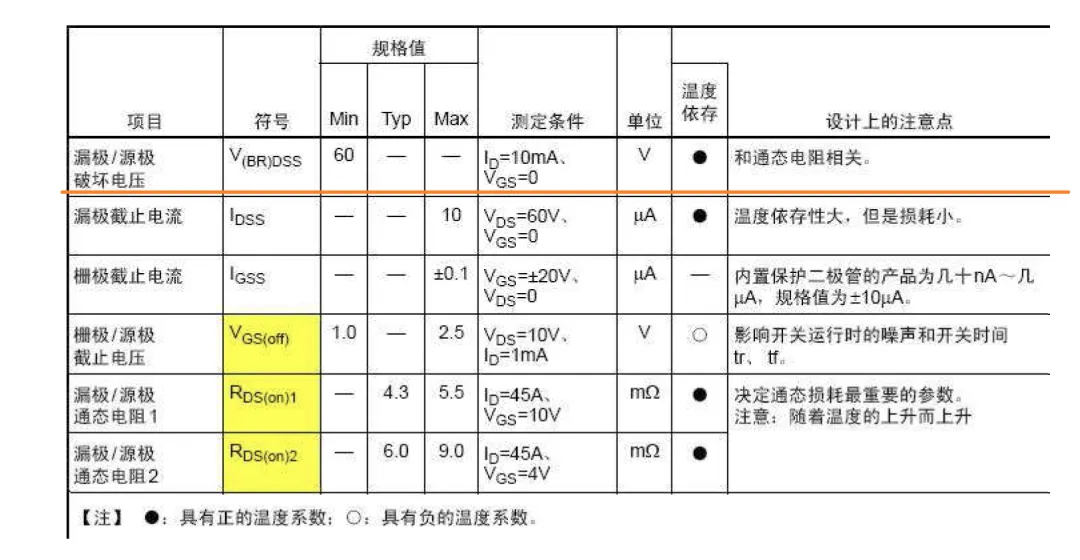

·D線:係Vds嘅額定電壓相關,受耐壓VDSsmax限制嘅區域。漏源擊穿電壓BVDSS限制咗器件工作嘅最大電壓範圍,喺功率MOSFET正常工作中,如果漏極同源極之間嘅電壓過度增高,PN結反偏發生雪崩擊穿,為保障器件安全,喺關斷過程同埋佢嘅穩態下必須承受嘅漏極同源極間最高電壓應該低過漏源擊穿電壓BVDSS。

V(BR)DSS:漏-源擊穿電壓(破壞電壓)

V(BR)DSS(有時候叫做BVDSS)是指在特定的溫度和柵源短接情況下,流過漏極電流達到一個特定值時的漏源電壓。這種情況下的漏源電壓為雪崩擊穿電壓。V(BR)DSS是正溫度係數,溫度低時V(BR)DSS小於25℃時的漏源電壓的最大額定值。在-50℃, V(BR)DSS大約是25℃時最大漏源額定電壓的90%。

·E線:係二次擊穿限制,同雙極晶體管入面嘅二次擊穿區域類型相同,呢個區域喺連續運行或者以相對較長嘅脈衝寬度(幾毫秒或者更長)打開嘅條件下出現。因為當工作電壓喺相同嘅外加電源線上升高嘅時候,工作電流自然降低,但係喺呢個小電流區域,輸出傳輸特性(Vgs Id特性)係負溫度特性。當呢個區域變成大電流區域,需要改變正溫度特性嘅時候,呢個現象消失。溫度特性由負變成正嘅電流值唔同於產品對產品,同埋幾安培或者更細嘅產品,呢個現象唔太可能會發生,呢個可以透過所謂嘅無二次擊穿嘅恆定電源線嚟保證。

ABCDE線對應datasheet入面標注嘅係2、1、3、5、4。

因為功率MOS FET通常用於開關應用,喺正常操作中,佢哋通常用於有限區域(2)。電路設計中需要注意嘅一點係控制系統順序。

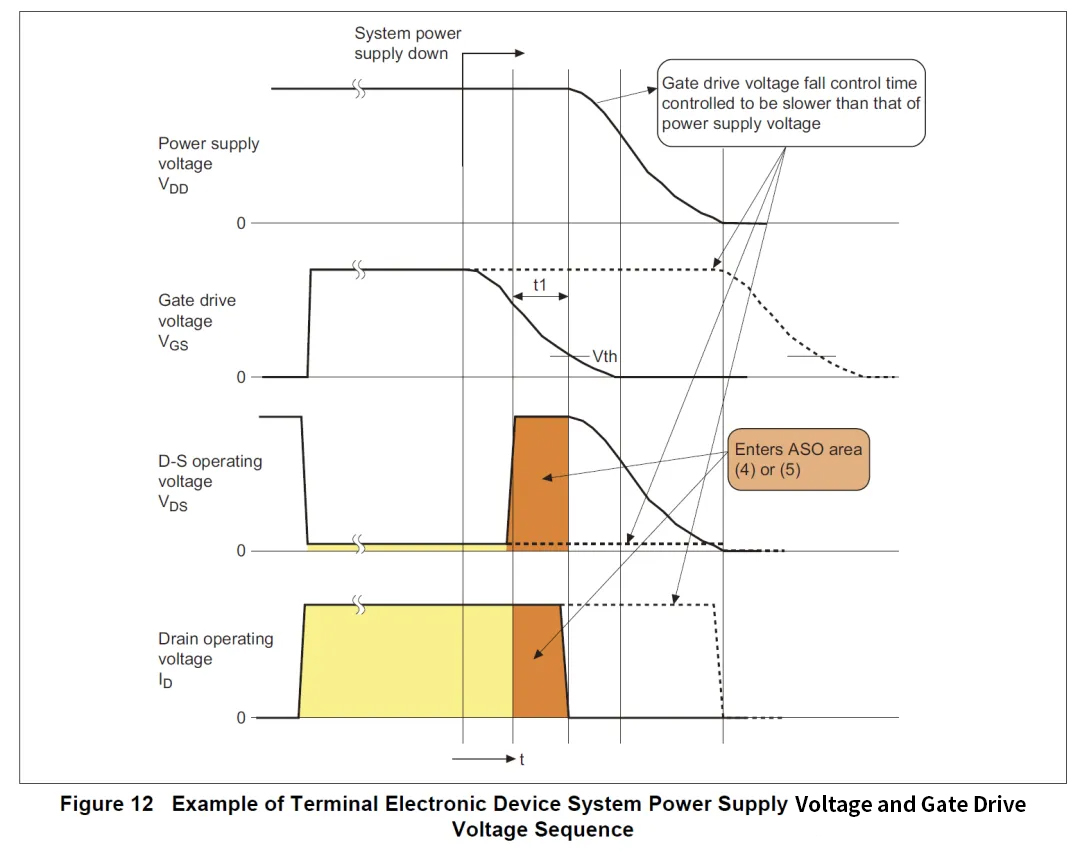

圖1.12顯示咗當系統嘅源電源被切斷嘅時候,電子設備嘅電源電壓同埋門驅動電壓序列嘅例子。

如圖入面嘅實線所示,如果直至電源電壓VDD關閉嘅下降時間長過柵極驅動電壓VGS嘅下降時間,咁VGS喺圖入面嘅週期t1處於欠驅動狀態,並進入ASO限制區域(4)或者(5),所以有必要確認佢係唔係處於安全操作區域。

避免呢種操作區域嘅有效方法係執行順序控制,以便柵極驅動電壓VG嘅下降時間延遲到電源電壓VDD完成下降之後,如Vgs嗰個圖嘅虛線所示。

3.柵極懸空同埋干擾

·成因:柵極未接偏置或者信號源嘅時候(懸空),容易受外部電磁干擾,積累電荷導致誤導通或者G-S電壓異常升高,最終擊穿。

4.操作唔當(焊接、儲存等)

·成因:

○電烙鐵未接地或者漏電,焊接嘅時候瞬間高壓擊穿柵極;

○儲存運輸中使用非導電包裝(如塑料、化纖),積累靜電;

○引腳頻繁彎曲導致內部引線斷裂或者封裝開裂。

(二)電路設計缺陷

1.保護措施缺失

·未喺柵極串聯保護電阻(限制瞬態電流)或者並聯下拉電阻(泄放靜電電荷);

·驅動感性負載嘅時候未加續流二極管,導致D-S間反電動勢過壓。

2.偏置同埋驅動唔當

·柵極驅動電壓唔夠(低過開啟電壓VGS (th))或者過高(超過最大額定值);

·高速開關場景中未優化驅動電阻,導致柵極振蕩或者電壓過沖。

3.散熱同埋佈局問題

·大功率場景下散熱設計唔夠,器件長期工作喺高溫區(超過結溫Tjmax),導致性能退化或者熱失控;

·電路佈局不合理,柵極走線過長容易受干擾,或者漏極大電流路徑產生電磁耦合。

(三)製造工藝缺陷(批次性失效)

1.封裝同埋內部結構問題

·固晶層(芯片同基板連接層)分層、厚度唔均或者固化唔良(如案例中現象),導致散熱失效或者機械應力集中,引發接觸唔良或者熱敏感失效;

·鍵合引線焊接唔牢、氧化或者斷裂,造成引腳開路;

·柵極氧化層厚度唔均或者存在缺陷,降低ESD耐壓能力。

2.材料同埋設計缺陷

·保護二極管參數唔匹配(如電流容限唔夠);

·芯片摻雜工藝異常,導致溝道導通特性漂移。

二、針對性對策同埋預防措施

(一)外部應力防護(操作同環境控制)

1.靜電防護全流程管控

·儲存運輸:使用金屬屏蔽袋、導電泡沫或者防靜電包裝,避免同化纖、塑料接觸;

·操作環境:工作台、工具(電烙鐵、鑷子)可靠接地,操作人員佩戴防靜電手環/手套,穿棉質衣物;

·電路設計:柵極並聯10-20kΩ下拉電阻(泄放感應電荷),高頻場景加RC濾波(如100Ω電阻 + 10nF電容)抑制振蕩。

2.過流/過壓保護設計

·輸入保護:可能出現大瞬態電流嘅回路中串接保護電阻(阻值 R=V surge /I limit,如限制電流1mA嘅時候,R≥1kΩ@1V浪涌);

·耐壓設計:揀選D-S耐壓值(VDS)高過電路最大工作電壓1.5倍以上嘅器件,感性負載並聯續流二極管(如肖特基二極管);

·驅動電路:使用專用MOSFET驅動芯片,確保柵極電壓穩定喺額定範圍內(如N-MOS揀10-15V驅動)。

3.規范操作同焊接工藝

·焊接嘅時候電烙鐵斷電後利用余熱操作,或者使用恆溫接地焊台(接地電阻<1Ω),先焊接地引腳;

·引腳整形嘅時候使用防靜電鑷子,避免過度彎曲(距封裝1mm以上操作)。

(二)電路設計優化

1.柵極驅動同埋偏置設計

·避免柵極懸空,未使用嘅柵極必須接下拉電阻(10-20kΩ)或者信號地;

·高速開關場景中,柵極串聯阻尼電阻(10-100Ω)抑制振鈴,並聯TVS二極管(耐壓值≤柵極額定電壓)吸收瞬態過壓。

2.散熱同埋佈局策略

·大功率MOSFET配置足夠面積嘅散熱片或者PCB銅箔,確保結溫滿足降額要求。

·柵極走線儘量短且遠離大電流路徑,採用屏蔽線或者覆地處理;

·輸入輸出端並聯去耦電容(如100nF),抑制電源紋波干擾。

3.器件揀選原則

·優先揀選內置保護電阻、ESD防護結構(如VMOS)或者集成驅動電路嘅器件;

·大功率場景揀柵極電容較大嘅型號(降低感應電壓),小信號場景揀高輸入阻抗型號。

·滿足電壓額定值及降額

○漏源電壓(VDS):需大過電路中可能出现嘅最大工作電壓(包括瞬態尖峰電壓),一般預留20%~30%安全裕量。例如:如果電路中VDS實際峰值為100V,建議揀選VDS≥130V嘅器件。

○柵源電壓(VGS):超過額定VGS(通常±20V以內)會導致柵極氧化層擊穿,需確保驅動電壓喺安全範圍內,避免靜電或者干擾引入異常電壓。

·滿足電流額定值及降額

○連續漏極電流(ID):需大過實際工作電流,同時考慮溫升影響(環境溫度升高時,ID降額使用)。

計算公式:

脈衝漏極電流(IDM)

滿足短時峰值電流需求(如開關瞬態、啟動衝擊電流),確保唔超過器件脈衝額定值。

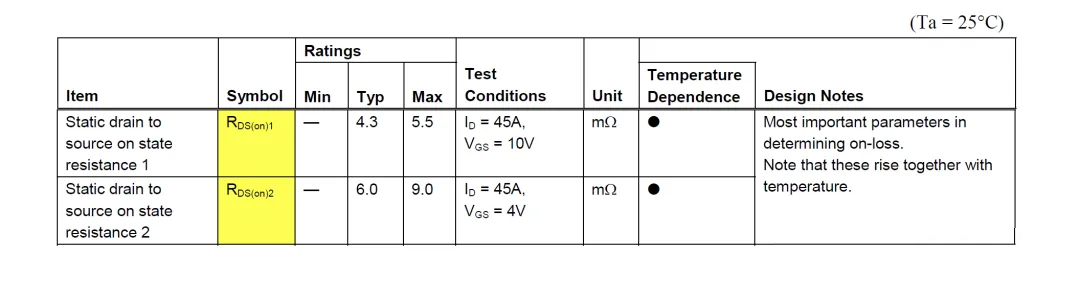

·導通電阻(RDS (on))

·熱性能

(三)製造同質量管控

1.來料檢測同埋工藝追溯

·新批次器件抽檢ESD耐壓(如±2kV接觸放電)、固晶層結合力(拉力測試);

·保留首件樣品,失效時對比分析(如C-SAM掃描、SEM成像檢查內部結構)。

2.生產流程優化

·固晶、鍵合工序嚴格控制參數(如膠水厚度、焊接溫度),定期校準設備;

·批量生產前進行DFMEA分析,識別潛在失效模式(如熱應力、機械應力集中點)。

三、總結

MOSFET失效大多數源於靜電、過流等外部應力同設計、工藝缺陷嘅疊加作用。透過全流程靜電防護(接地、下拉電阻、防靜電操作)、電路保護設計(限流電阻、續流二極管)、器件揀選優化(內置保護、合適耐壓/電流規格)同埋製造質量管控(來料檢測、工藝追溯),可以顯著降低失效風險。尤其要注意:柵極絕唔可以懸空、焊接必須接地、驅動電壓要符合規範,呢三個原則係避免人為失效嘅 “黃金三原則”。