先進封裝 (AP) 係指將集成電路 (IC) 進行封裝,從而提升效能嘅各種創新技術。相較於傳統封裝,佢具有高度集成、工藝方法更加多元,以及更佳嘅導電同散熱性能等優點。

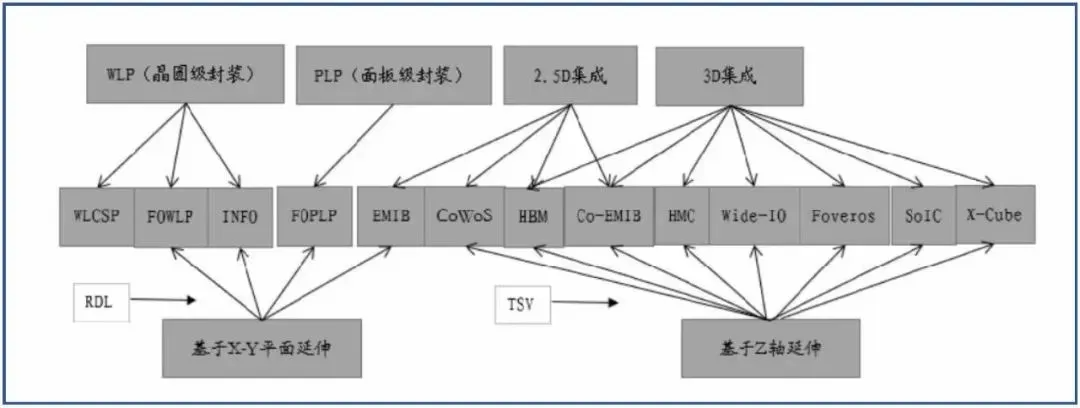

先進封裝嘅結構大致包括:覆晶 (Flip-Chip,FC)、2.5D封裝與3D封裝、晶圓級封裝(Wafer Level Package,WLP)、系統級封裝(SiP)、Chiplet。

先進封裝嘅工藝大致含有:Bump(凸塊)工藝、RDL(重分佈層)工藝、TSV(矽通孔)工藝。

一、先進封裝結構

覆晶 (Flip Chip)

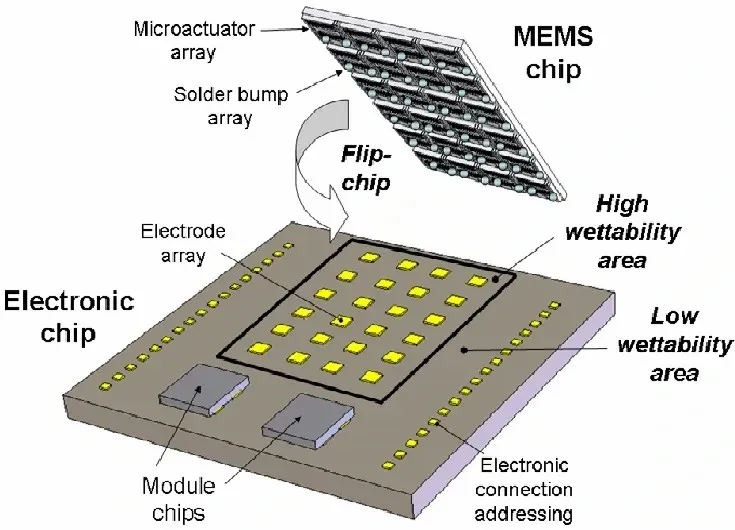

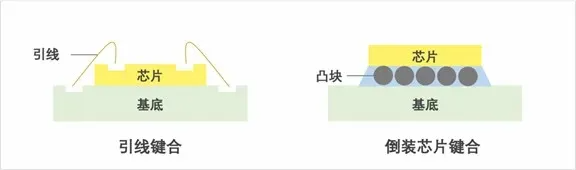

喺傳統封裝技術入面,晶片會被封裝喺底部,並通過金線連接到封裝基板上。而覆晶技術則將晶片直接翻轉並安裝喺封裝基板上,然後使用微細嘅焊點或導電膠水進行連接。呢種封裝技術具有較高嘅訊號密度、較細嘅體積、高速傳輸同良好嘅熱傳導性能,因此喺半導體行業得到咗廣泛應用。

2.5D封裝與3D封裝

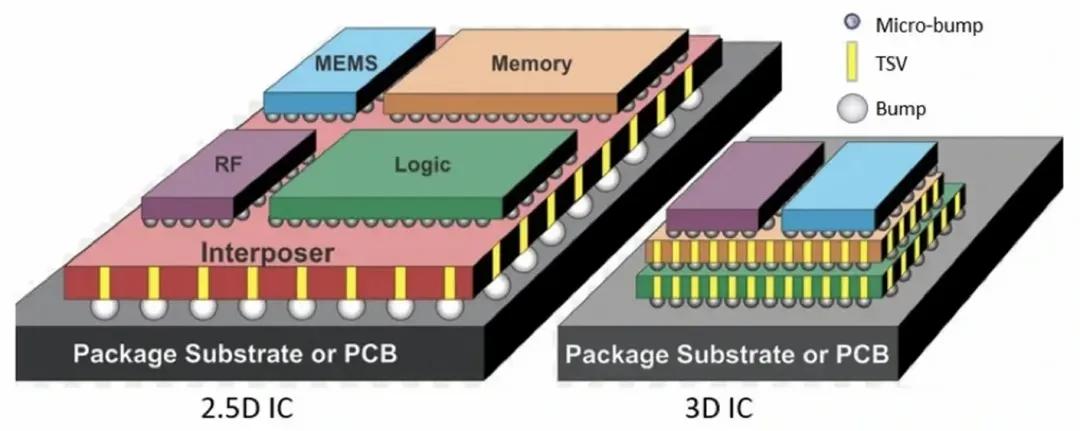

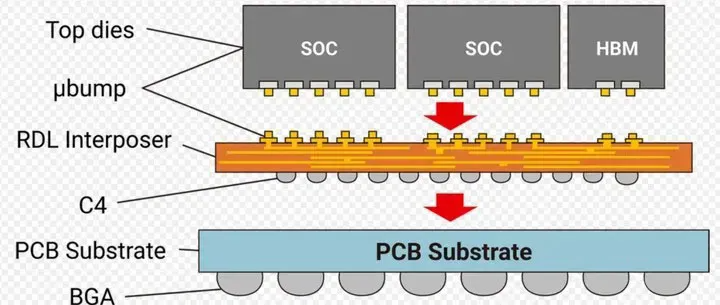

· 2.5D封裝:採用矽或者重分佈層 (RDL) 扇出嘅中介層,被用於喺SoC嘅裸晶之間路由訊號。

· 3D封裝:採用混合鍵合或以上技術嘅某種組合嚟實現晶片嘅垂直堆疊。

2.5D/3D堆疊封裝涉及垂直堆疊多個裸晶或晶片,形成三維結構。呢個平台可實現更高嘅集成度、更高嘅性能同更細嘅外形尺寸,使其成為應對人工智能、5G同HPC應用挑戰嘅重要技術。

晶圓級封裝

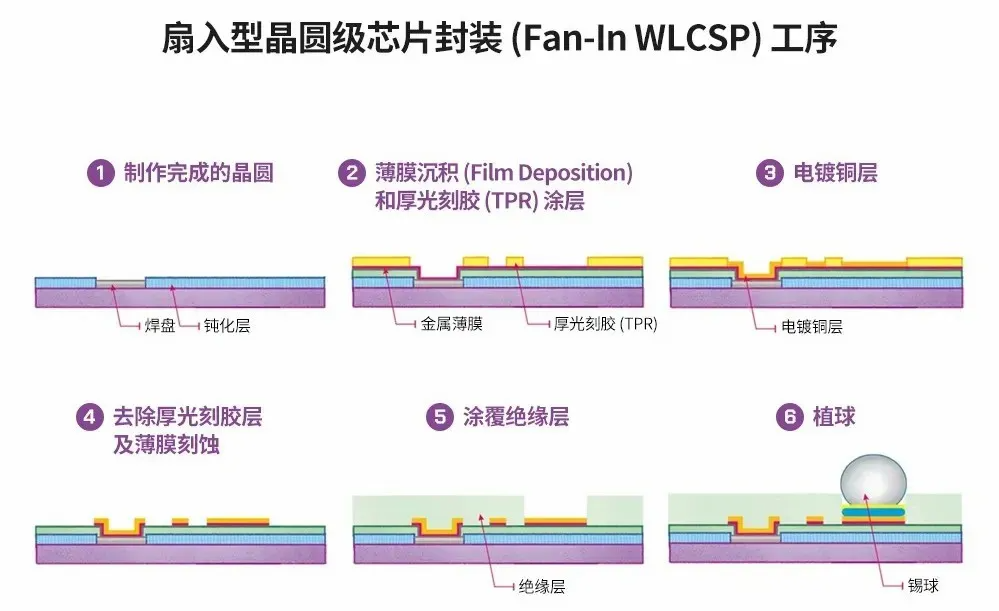

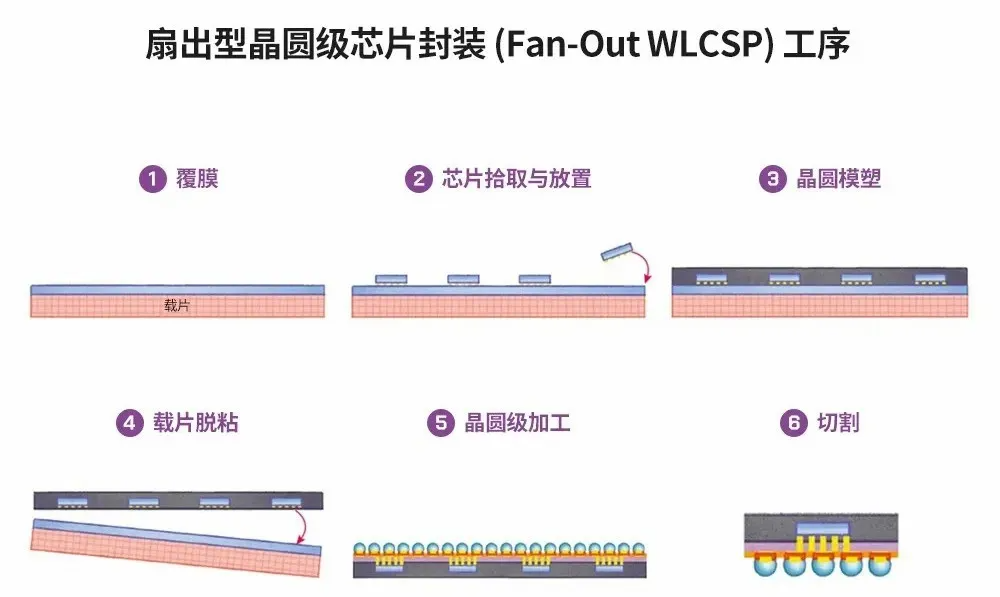

晶圓級封裝係喺切割晶圓成單個晶片之前,喺成個晶圓上進行封裝過程。晶圓級封裝分為扇入型晶圓級晶片封裝(Fan-In WLCSP)同扇出型晶圓級晶片封裝(Fan-Out WLCSP),其特點係喺成個封裝過程中,晶圓始終保持完整。

系統級封裝(SiP)

系統級封裝(SiP)技術係通過將多個裸晶(Die)及無源器件整合喺單個封裝體內嘅集成電路封裝技術。喺後摩爾時代,系統級封裝(SiP)技術可以幫助晶片成品增加集成度、減細體積並降低功耗。

Chiplet

Chiplet係一種集成電路設計同封裝方法,佢將一個晶片(稱為主晶片)與多個輔助晶片(稱為chiplet)集成喺一齊,以形成一個功能完整嘅系統。Chiplet技術嘅出現係為咗解決集成電路尺寸同複雜性不斷增加所帶嚟嘅挑戰,提高系統集成度、性能同靈活性。

二、先進封裝工藝

Bump(凸塊)工藝

凸塊製造技術(Bumping)係喺晶片上製作凸塊,通過喺晶片表面製作金屬凸塊提供晶片電氣互連嘅“點”介面,廣泛應用於FC、WLP、CSP、3D等先進封裝。Bumping工藝介於產業鏈前道集成電路製造同後道封裝測試之間,係先進封裝嘅核心技術之一。

RDL(重分佈層)工藝

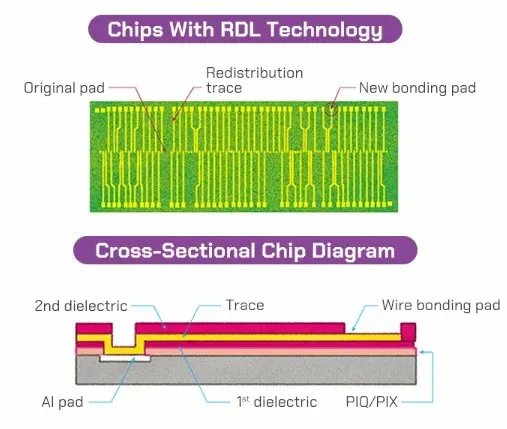

RDL係指重新佈線嘅行為。該工藝嘅目的係通過添加額外嘅金屬層嚟重新排列晶圓上已經形成嘅鍵合墊。RDL技術係一種晶圓級工藝,只重新配置焊盤,經過RDL嘅晶圓要經過傳統嘅封裝工藝嚟完成封裝。下圖顯示咗使用RDL技術將襯墊重新分配到邊緣嘅中心襯墊晶片嘅示意圖同橫截面結構。

TSV(矽通孔)工藝

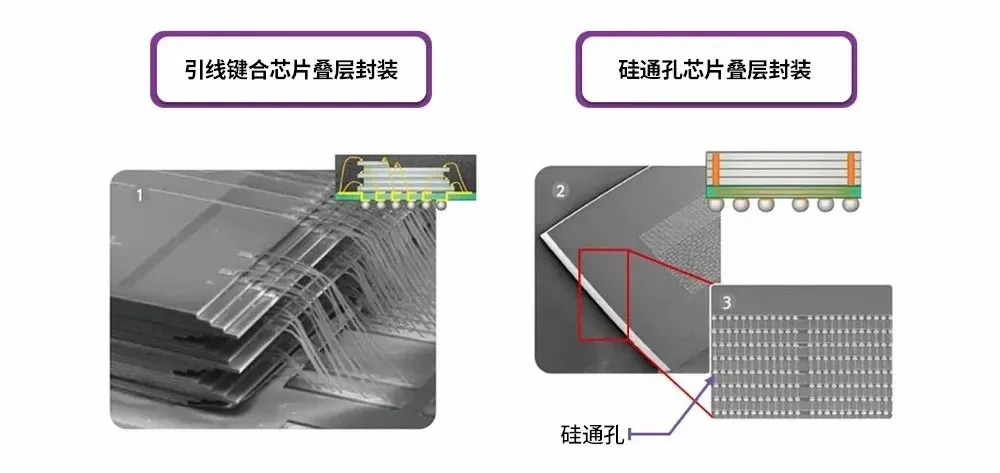

矽通孔係一種通過喺矽片上鑽孔嚟容納電極嘅晶片堆疊技術。矽通孔封裝嘅主要優勢在於性能優越且封裝尺寸較細。相比採用傳統引線方法實現晶片與晶片互連或晶片與基板互連,矽通孔通過喺晶片上鑽孔並填充金屬等導電材料嚟實現晶片垂直互連。

使用矽通孔技術嘅晶片剖面圖(ⓒ HANOL出版社)