DC-DC 於單板設計中,是數字電路不可或缺的一環。筆者於工作中曾遇過以下情況:DC-DC 位置因太貼近模擬電路,導致模組干擾了音頻訊號;又或將 DC-DC 置於熱敏感元件背面,結果電感發熱損壞了塑膠件;更有因功率電感靠近線纜,而令傳導發射(Conducted Emission)持續超出標準的問題。

那麼,究竟如何才能做好一個開關電源(Switching Power Supply)的佈局(Layout)?本文主要從以下三個方面作出探討:

1. 電源模組的擺放位置與疊層(Stack-up)設計

2. 功率元件的佈局

3. 控制訊號的走線

01、電源模組擺放位置與疊層設計

電源模組的擺放位置與疊層設計,是 DC-DC 設計的首要考慮。

(1) 電源模組擺放位置

電源模組應盡量就近負載(Load),以減小輸出阻抗及線纜對外的輻射干擾。

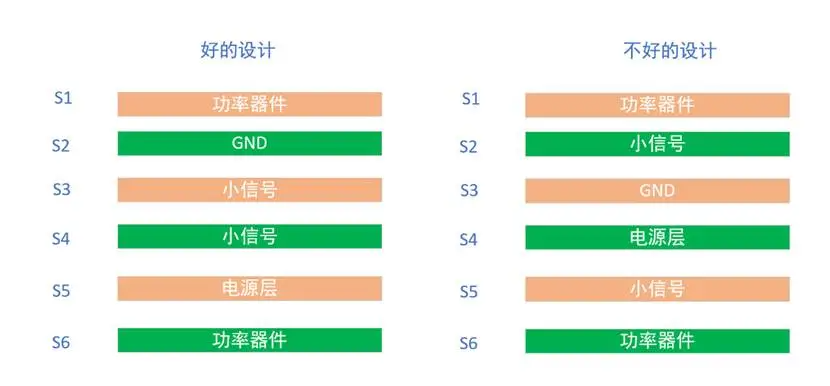

(2) PCB 疊層設計

兩種設計方案最主要之分別,在於小訊號層的安排。若將小訊號層置於功率層(Power Plane)與接地層(GND Plane)之間,小訊號線路便會與功率元件之間產生電容性雜訊耦合(Capacitive Noise Coupling)。而在推薦的設計中,小訊號層被兩個接地層所屏蔽,有效隔絕了干擾。

02、功率元件的佈局

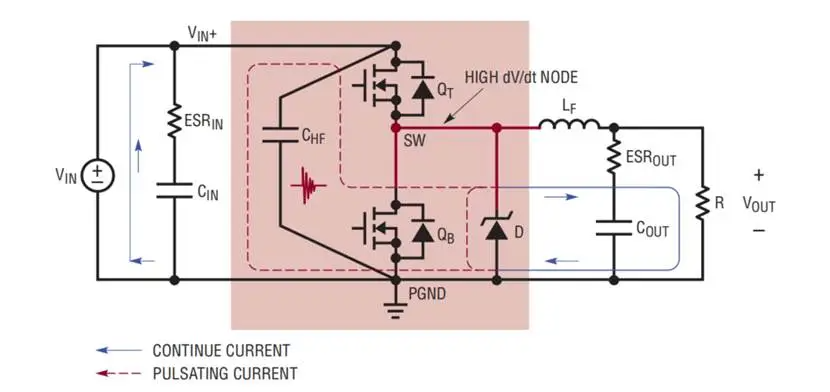

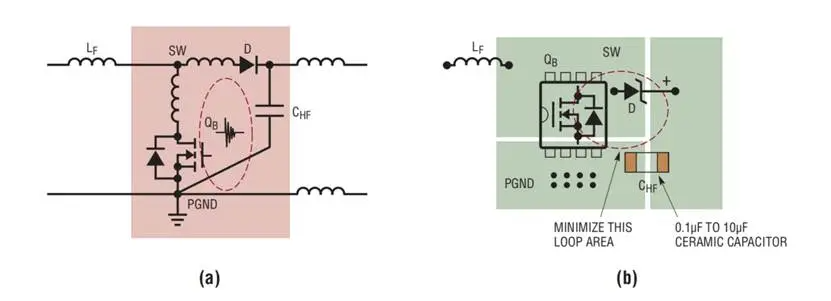

核心原則:功率迴路面積最小化。

功率迴路中存在高速變化的 dv/dt(電壓變化率)與 di/dt(電流變化率),迴路面積越大,變化的電場與磁場對外輻射便越強。

同時,元件焊接後會在 PCB 上形成寄生電感(Parasitic Inductance),走線越長,寄生電感越大。這些寄生電感在高速 di/dt 的作用下,會在 MOSFET 開通和關斷時形成振鈴(Ringing)。振鈴不僅會增加元件的損耗,嚴重時更可能直接損壞功率 MOSFET。

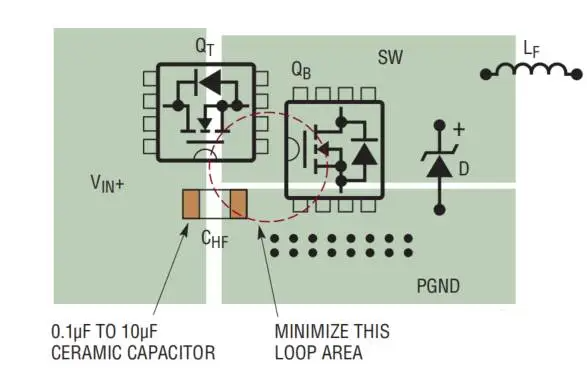

推薦佈局如下:

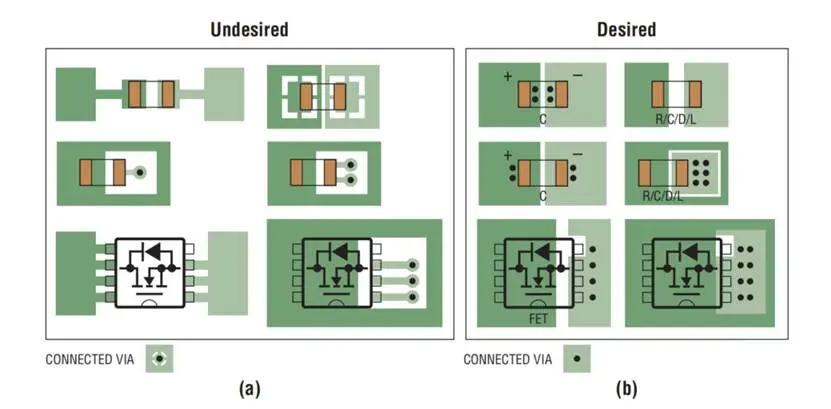

增加功率元件的連接點,以最小化阻抗。

推薦的佈局方式能大幅降低 PCB 的寄生電感,以及元件焊盤與 PCB 銅箔之間的阻抗,從而使電壓降(Voltage Drop)最小化。

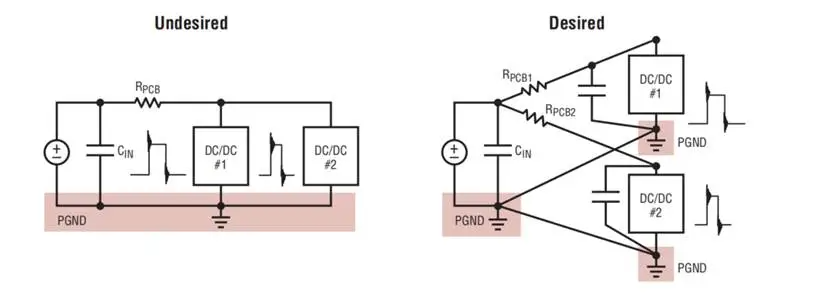

多路電源佈局時,輸入電流走線需分開,以避免共地干擾(Common Ground Interference)。

03、控制電路的佈局

控制電路的佈局主要有兩大要點:

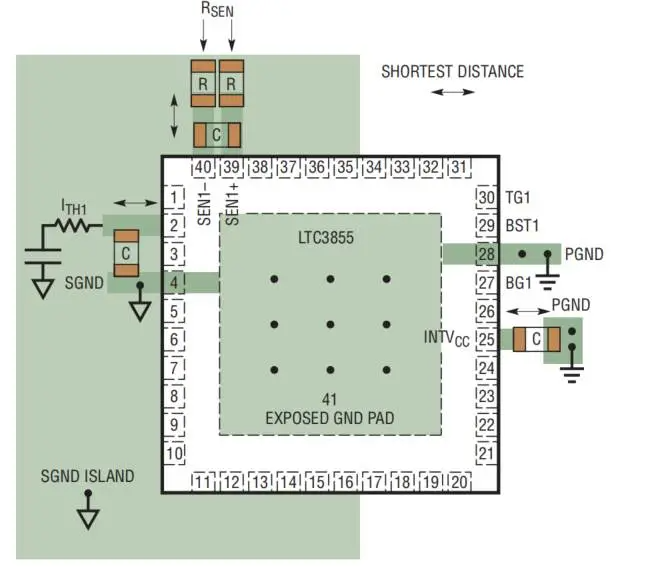

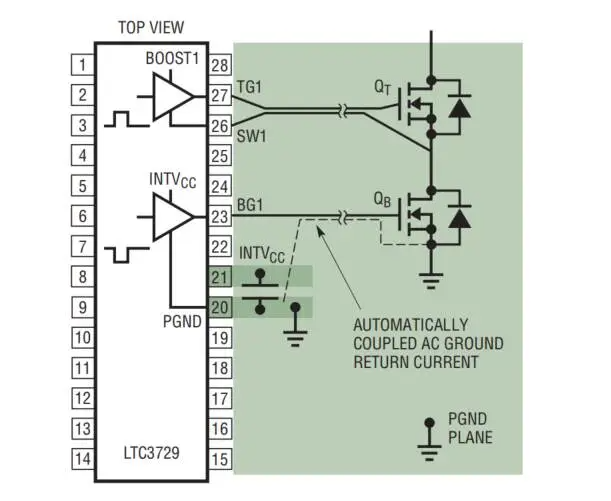

1. 訊號地(Signal Ground)與電源地(Power Ground)分離。

2. 控制器的去耦電容(Decoupling Capacitor)需盡量靠近元件的管腳放置。

此外,驅動電路(Driver Circuit)的面積應盡可能縮小,其走線亦應盡量短。這樣做既可以降低阻抗,亦能減少在閘極(Gate)引入的寄生參數。曾處理 EMC 問題的工程師應該都知道,縮短驅動線的長度、避免穿層,能極大地改善開關節點(SW Node)的波形。

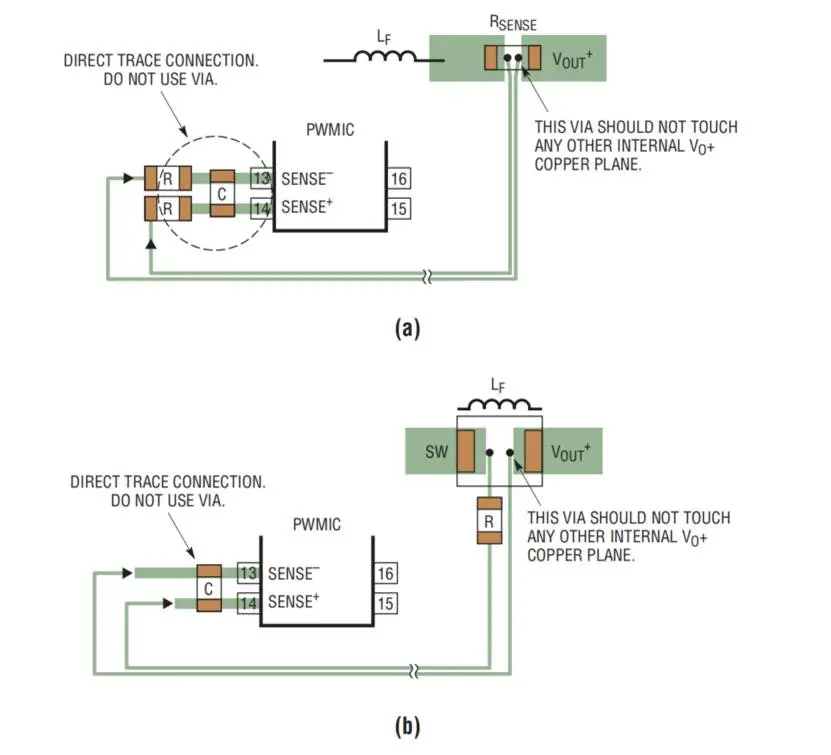

對於敏感訊號的採樣電阻(Sampling Resistor),應使用開爾文連接(Kelvin Connection)的方式。若其中一端為接地(GND),同樣應以差分訊號(Differential Signal)的形式走線,以降低環路面積和共模干擾(Common-mode Interference)。

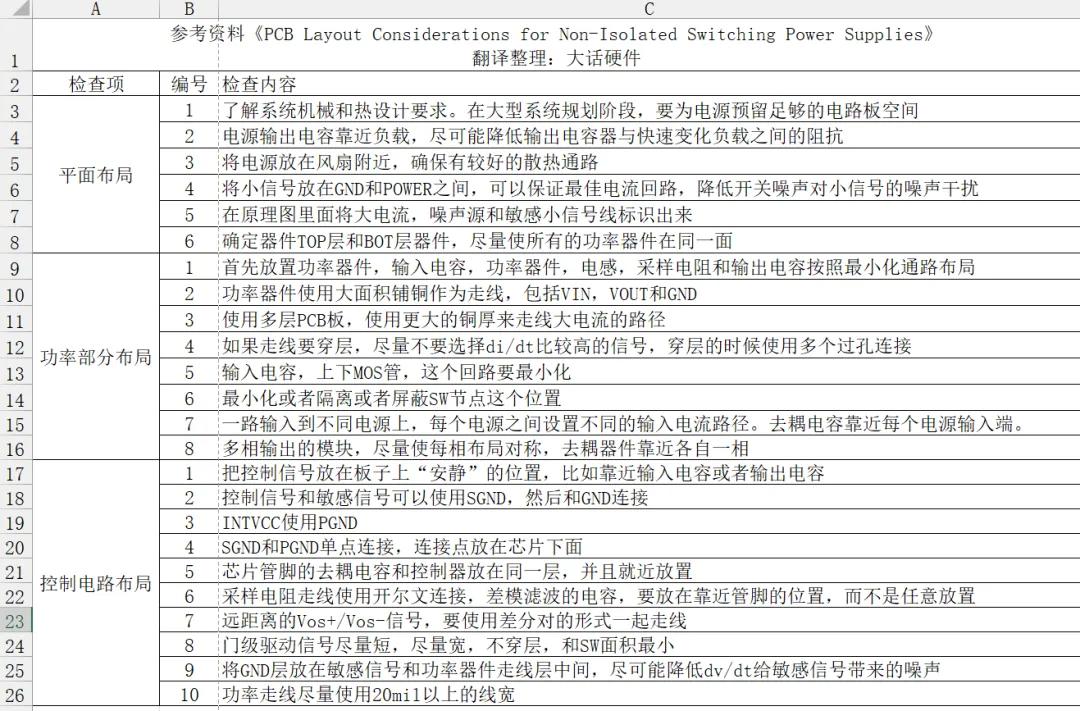

綜上所述,可將佈局要求整理如下: