DC-DC轉換器(直流-直流轉換器)喺單板設計中,係數碼電路不可或缺嘅部分。工作上遇到過因為DC-DC位置離模擬電路太近,搞到模組干擾咗音訊;DC-DC位置放喺熱敏感器件背面,搞到因為電感發熱整爛咗塑膠件;仲有因為功率電感靠近線纜,傳導發射一直超標嘅問題。

咁點樣先可以做好一個開關電源嘅佈局?本文主要從3個方面考慮:

1、電源模組放置位置同疊層設計

2、功率器件嘅佈局

3、控制訊號嘅走線

01、電源模組放置位置同疊層設計

喺電源模組放置嘅位置同疊層設計係DC-DC設計嘅關鍵。

(1)電源模組盡量考慮負載,減小輸出阻抗同線纜對外嘅輻射。

(2)PCB疊層設計

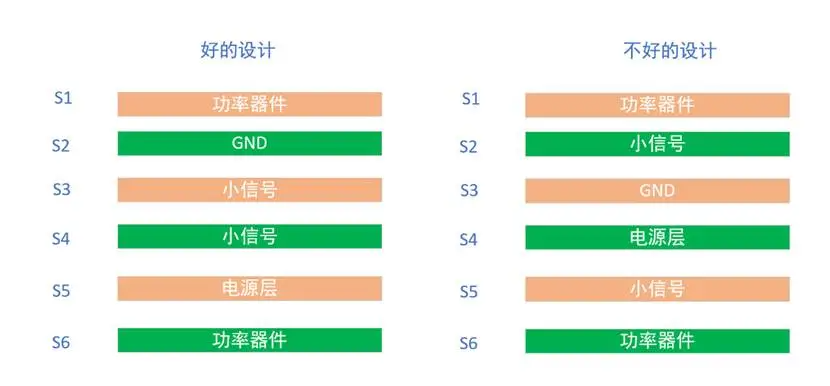

兩種設計最主要嘅差別係細訊號位置。如果將細訊號放喺功率層同GND之間,細訊號同功率器件之間存在容性雜訊耦合。而喺推薦嘅設計中,兩個細訊號被GND進行咗屏蔽。

02、功率器件嘅佈局

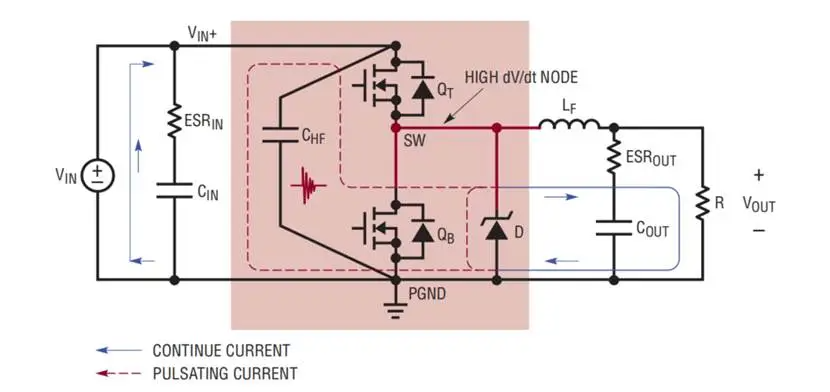

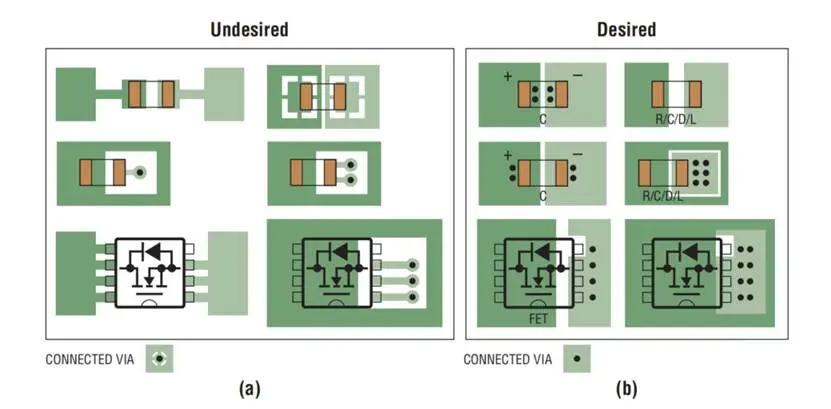

功率器件面積最小化。功率器件迴路中存在快速變化嘅dv/dt同di/dt,面積越大,變化嘅電場同磁場對外嘅輻射越強。

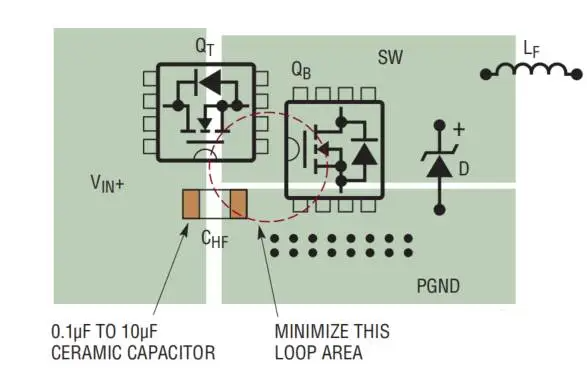

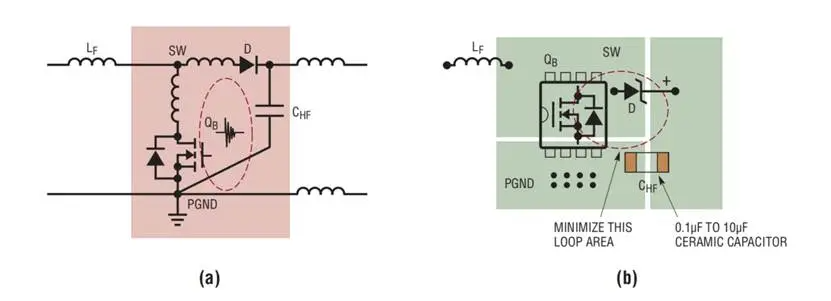

同時,器件焊接後會喺PCB板上形成寄生電感。走線越長,寄生電感越大。呢啲寄生電感喺di/dt下,會喺MOS管開通同關斷嘅時候形成振鈴。振鈴會增加器件嘅損耗,甚至係損耗功率MOSFET。推薦如下佈局:

功率器件增加連接點以最小化阻抗。

推薦嘅設計,能極大咁降低PCB寄生電感同器件焊盤與PCB銅箔嘅阻抗,使得電壓降最小化。

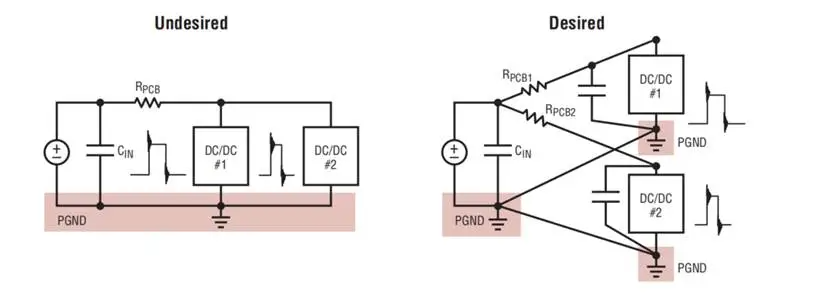

多路電源佈局時,輸入電流走線需要分開,避免共地干擾。

03、控制電路嘅佈局

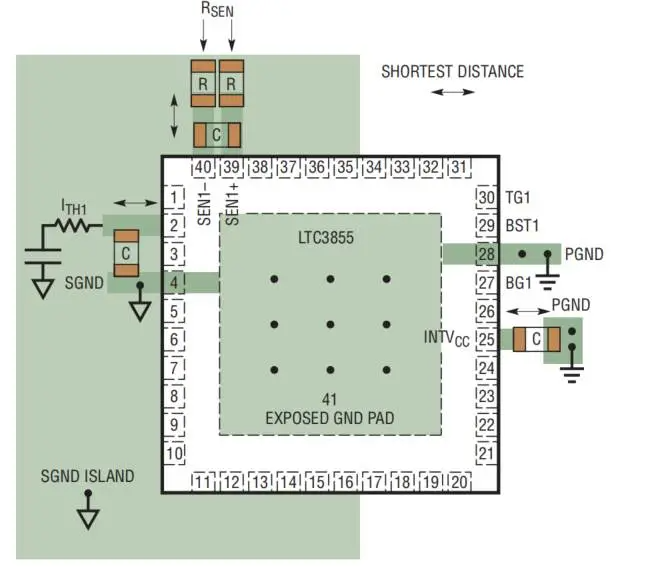

控制電路佈局主要有兩點:訊號地同電源地分離,控制器嘅去耦電容靠近器件管腳放置。

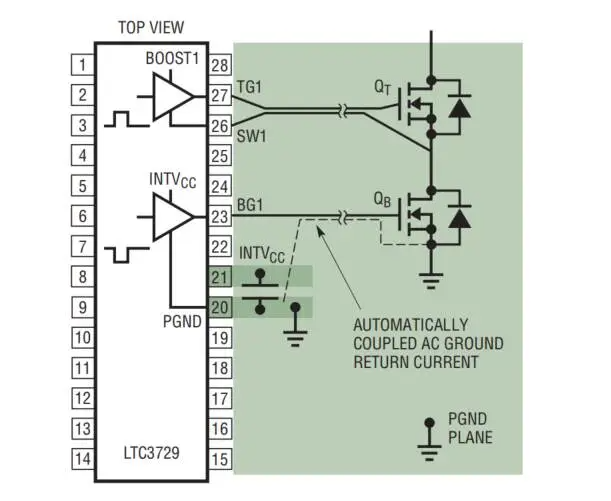

驅動電路面積盡可能嘅細,驅動電路走線盡量短。咁樣做既可以降低阻抗,仲可以減小喺柵極引入嘅寄生參數。整改過EMC問題嘅同學應該知道,減小驅動線嘅長度,唔穿層,能極大咁改善SW處嘅波形。

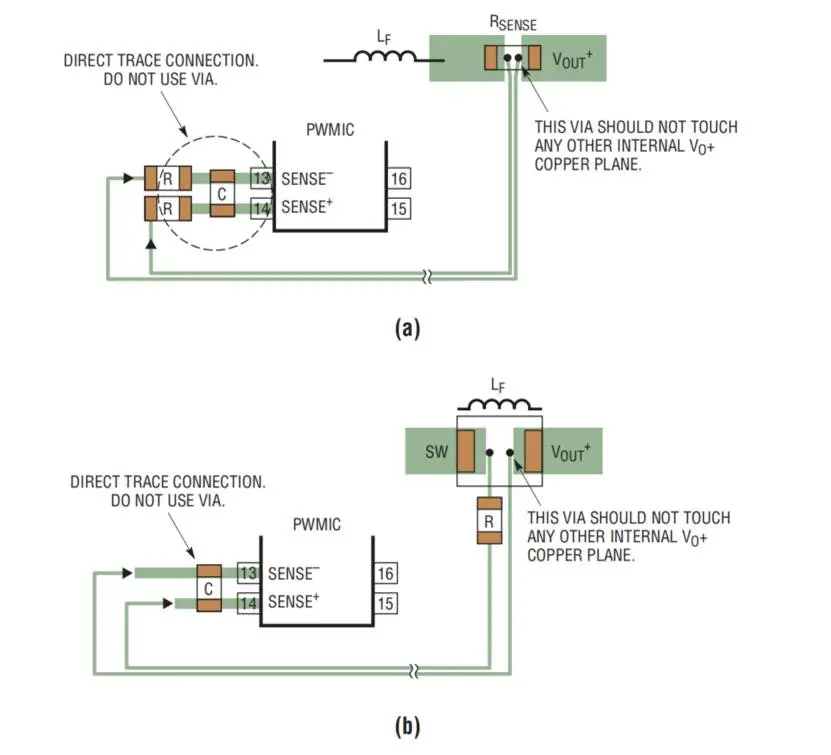

敏感訊號採樣電阻使用開爾文連接嘅方式。如果一端係GND,同樣要以差分訊號嘅形式走線,降低環路面積同共模干擾。

佈局要求整理成佈局要求如下:

| 檢查項 | 編號 | 檢查內容 |

| 平面佈局 | 1

| 瞭解系統機械和熱設計要求。在大型系統規劃階段,要為電源預留足夠的電路板空間 |

| 2 | 電源輸出電容靠近負載,盡可能降低輸出電容器與快速變化負載之間的阻抗 |

| 3 | 將電源放在風扇附近,確保有較好的散熱通路 |

| 4 | 將小信號放在GND和POWER之間,可以保證最佳電流回路,降低開關雜訊對小信號的雜訊干擾 |

| 5 | 在原理圖裏面將大電流,雜訊源和敏感小信號線標識出來 |

| 6 | 確定器件TOP層和BOT層器件,儘量使所有的功率器件在同一面 |

| 功率部分佈局 | 1 | 首先放置功率器件,輸入電容,功率器件,電感,採樣電阻和輸出電容按照最小化通路佈局 |

| 2 | 功率器件使用大面積鋪銅作為走線,包括VIN, VOUT和GND |

| 3 | 使用多層PCB板,使用更大的銅厚來走線大電流的路徑 |

| 4 | 如果走線要穿層,儘量不要選擇di/dt比較高的信號,穿層的時候使用多個過孔連接 |

| 5 | 輸入電容,上下MOS管,這個回路要最小化 |

6

| 最小化或者隔離或者遮罩SW節點這個位置 |

| 7 | 一路輸入到不同電源上,每個電源之間設置不同的輸入電流路徑。去耦電容靠近每個電源輸入端。 |

| 8 | 多相輸出的模組,儘量使每相佈局對稱,去耦器件靠近各自一相 |

| 控制電路佈局 | 1 | 把控制信號放在板子上“安靜”的位置,比如靠近輸入電容或者輸出電容 |

| 2 | 控制信號和敏感信號可以使用SGND,然後和GND連接 |

| 3 | INTVCC使用PGND |

| 4 | SGND和PGND單點連接,連接點放在晶片下麵 |

| 5 | 晶片管腳的去耦電容和控制器放在同一層,並且就近放置 |

| 6 | 採樣電阻走線使用開爾文連接,差模濾波的電容,要放在靠近管腳的位置,而不是任意放置 |

| 7 | 遠距離的Vos+/Vos-信號,要使用差分對的形式一起走線 |

| 8 | 門級驅動信號儘量短,儘量寬,不穿層,和SW面積最小 |

| 9 | 將GND層放在敏感信號和功率器件走線層中間,盡可能降低dv/dt給敏感信號帶來的雜訊 |

| 10 | 功率走線儘量使用20mil以上的線寬 |